Filter Design HDL Coder generates synthesizable, portable VHDL® and Verilog® code for implementing fixed-point filters designed with MATLAB on FPGAs or ASICs. It automatically creates VHDL and Verilog test benches for simulating, testing, and verifying the generated code.

Get Started:

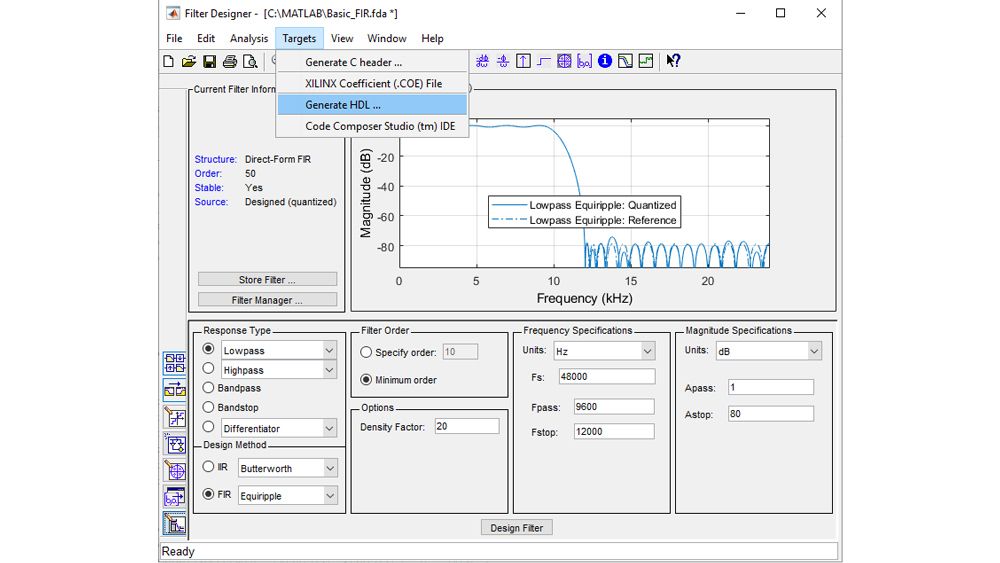

Filter Design HDL Coder is integrated with DSP System Toolbox to provide a unified design and implementation environment. You can design filters and generate VHDL and Verilog code either from the MATLAB command line or from DSP System Toolbox using the Filter Designer app or the Filter Builder app.

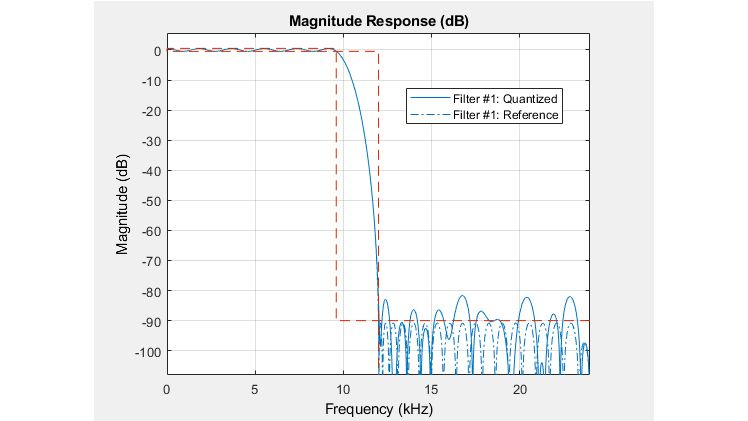

The design entry input to Filter Design HDL Coder is a quantized filter that you create in one of two ways:

- Design and quantize the filter with DSP System Toolbox

- Design the filter with Signal Processing Toolbox and then quantize it with DSP System Toolbox

Filter Design HDL Coder supports several important filter structures, including:

Discrete-time finite impulse response (FIR), which includes symmetric, anti-symmetric, and transposed structures

Second-order section (SOS) infinite impulse response (IIR), which includes direct form I, II, and transposed structures

Multirate filters, which includes cascaded integrator-comb (CIC) interpolator and decimator, direct-form FIR and transposed FIR polyphase interpolator and decimator, FIR hold and linear interpolator, and FIR polyphase sample rate converter structures

Fractional delay filters, which includes Farrow structures

Filter Design HDL Coder can generate HDL code from cascaded multirate and discrete-time filters. Each of these single-rate and multirate filter structures supports fixed-point and floating-point (double precision) realizations. In addition, the FIR structures support unsigned fixed-point coefficients.

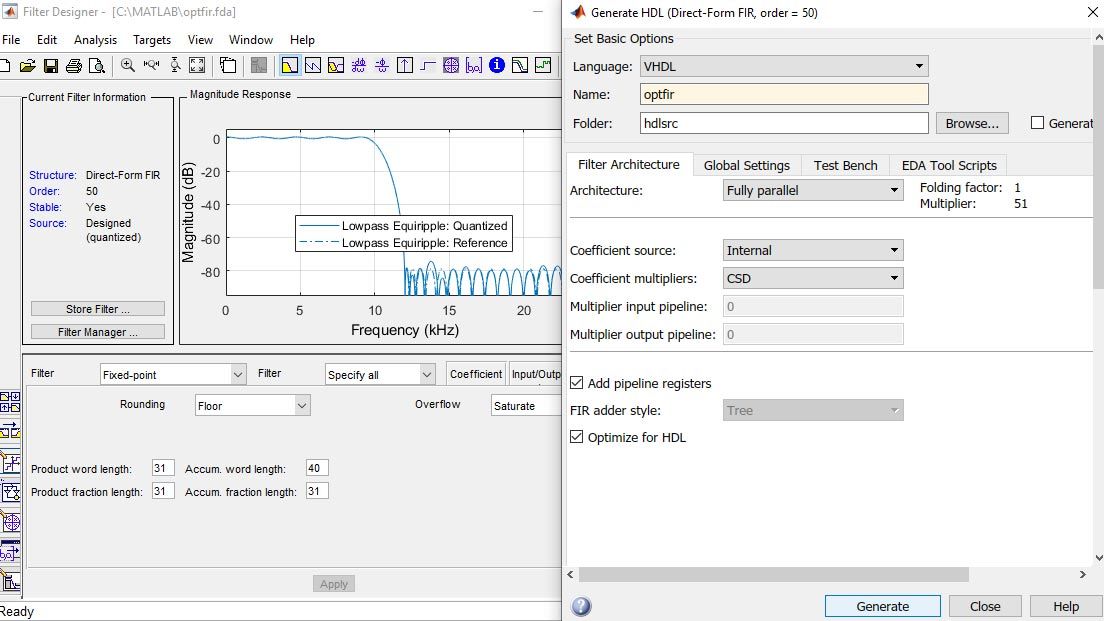

You can generate VHDL or Verilog code for fixed-point filters from either the Filter Designer app or the Filter Builder app. When generating HDL code from either app, you can set HDL generation options to specify the implementation architecture, select port data types, insert pipeline registers, and more. Other options let you generate and configure a test bench for your filter HDL design.

Filter Design HDL Coder generates filter and test bench HDL code for a quantized filter based on an option setting or on property name and property value pairs. These settings let you:

- Name language elements

- Specify port parameters

- Use advanced HDL coding features

All properties have default settings. You can customize the HDL output by adjusting the settings with the Filter Design and Analysis app or the Filter Builder app. The apps let you set properties associated with:

- HDL language specification

- File name and location specifications

- Reset specifications

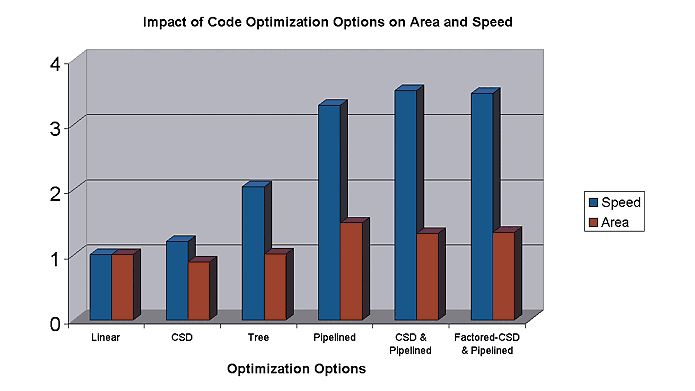

- HDL code optimizations

- Test bench customizations

You can generate a VHDL or Verilog test bench to simulate and test the generated HDL code. Additionally, with HDL Verifier, you can generate a Simulink cosimulation block to connect your behavioral filter model and tests running in Simulink to the generated HDL running in the Cadence® Incisive® and Xcelium™ simulators, or the Mentor® ModelSim® and Questa® simulators. Cosimulation simplifies verification of your filter design by enabling you to directly compare results from the generated HDL code and results from a behavioral filter model running in Simulink. This integration lets you apply the advanced analysis and visualization capabilities of MATLAB and Simulink to test, debug, and verify the HDL implementation of your filter designs.