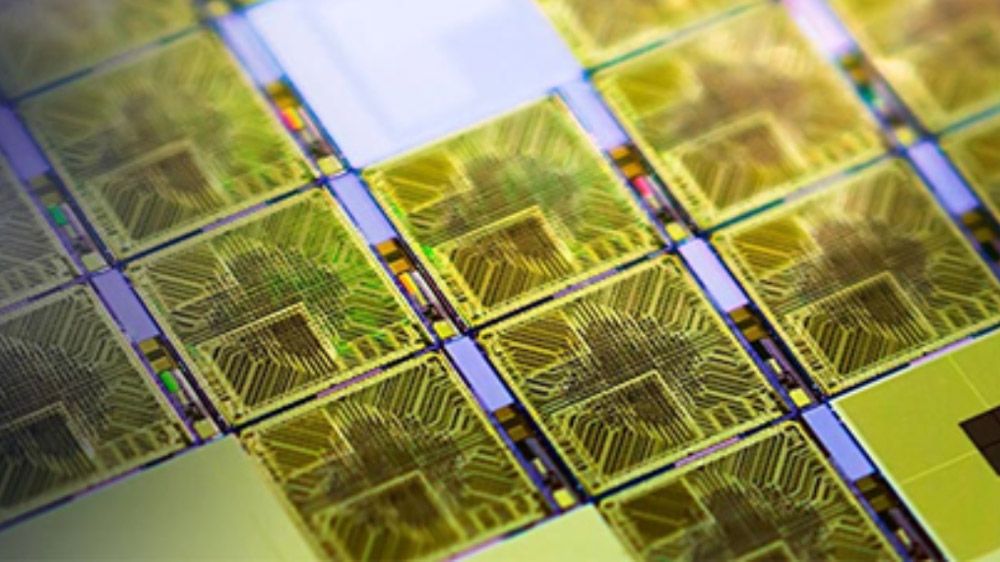

HDL Verifier lets you test and verify VHDL® and Verilog® designs for FPGAs, ASICs, and SoCs. You can verify RTL with testbenches running in MATLAB or Simulink using cosimulation with Siemens® Questa™ or ModelSim™, Cadence® Xcelium®, and the AMD® Vivado® simulator. You can reuse these same testbenches with FPGA development boards to verify hardware implementations.

HDL Verifier generates SystemVerilog verification models for RTL testbenches and complete Universal Verification Methodology (UVM) environments. These models run natively in the Questa, Xcelium, and Vivado simulators, as well as Synopsys® VCS® via the SystemVerilog Direct Programming Interface (DPI).

HDL Verifier provides tools for debugging and testing implementations on AMD, Intel®, and Microchip boards from MATLAB. You can insert probes into designs and set trigger conditions to upload internal signals into MATLAB for visualization and analysis.

RTL Verification

Verify HDL code for ASICs or FPGAs with a MATLAB and Simulink testbench through cosimulation with HDL simulators. Generate SystemVerilog testbenches for verification environments used in unit- or chip-level testing.

FPGA Prototyping, Verification, and Testing

Perform hardware-based verification on FPGA development boards using FPGA-in-the-loop testing. Probe internal signals within designs for hardware debugging, and control testing from MATLAB.

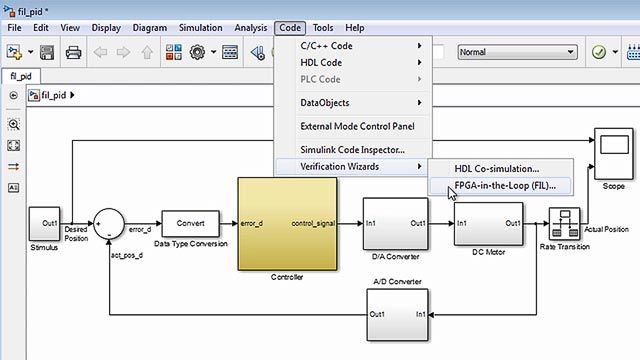

HDL Cosimulation

Verify HDL code using MATLAB and Simulink as a testbench. Incorporate legacy HDL into system simulations through cosimulation with HDL simulators including ModelSim and Questa, Xcelium, and the Vivado simulator.

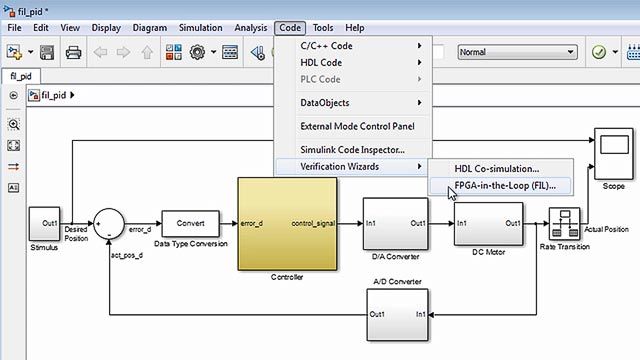

FPGA-in-the-Loop

Use MATLAB and Simulink testbenches to test HDL implementations executing on FPGA boards. Connect your host computer automatically to AMD, Intel, and Microchip FPGA boards over Ethernet, JTAG, or PCI Express®.

Generate SystemVerilog DPI

Use ASIC Testbench to generate SystemVerilog DPI components from MATLAB functions or Simulink subsystems for use in functional verification environments, including VCS, Xcelium, and ModelSim or Questa.

Generate UVM Environments

Use ASIC Testbench to generate complete Universal Verification Methodology (UVM) testbenches from Simulink models. Generate UVM sequences, scoreboards, and predictors, and then incorporate them into production testbenches based on Questa, Xcelium, VCS, or the Vivado simulator.

FPGA Data Capture

Capture high-speed signals from designs executing on an FPGA and automatically load them into MATLAB for visualization and analysis. Analyze signals throughout your design to verify expected behavior or investigate anomalies.

AXI Manager

Access on-board memory from MATLAB and Simulink over JTAG, Ethernet, or PCI Express. Test FPGA algorithms via read or write access to AXI4 registers and transfer large image or signal files between MATLAB and Simulink and on-board memory locations.

Documentation | Examples (AMD, Intel)

Generate SystemC TLM 2.0 compatible transaction-level models

Use ASIC Testbench to generate SystemC virtual prototype models with TLM 2.0 interfaces for use in virtual platform simulations. Use TLM generator to produce IP-XACT files with mapping information between Simulink and generated TLM components.

Product Resources:

“Simulink allows for us to reduce time spent on hand-writing production UVM test benches, test sequences and scoreboards by about 50% – leaving more time for us to focus on application for breakthrough innovations. Our ASICs designed for automotive applications rely on UVM for production verification – MATLAB and Simulink simplify the once tedious task of developing the algorithms for these devices.”

Khalid Chishti, Allegro MicroSystems